# **Cipher-510 Hardware Reference Manual**

V1.2

Jun 6, 1996

© 1996, Syntech Information Corporation CipherLab™ is a registered trademark of the Syntech Information Corporation

# TABLE OF CONTENTS

| 1. Preface                             | 1   |

|----------------------------------------|-----|

| 2. General Features                    | 2   |

| 3. Characteristics                     | 3   |

| 3.1. Electrical                        | 3   |

| 3.2. Environmental                     | 3   |

| 3.3. Physical                          | 3   |

| 4. Nomenclature                        | 4   |

| 5. PCB                                 | 6   |

| 6. Power Circuit                       | 7   |

| 6.1. Power Source                      | 7   |

| 6.2. Switching Regulator               | 8   |

| 6.3. Operation Battery                 | 8   |

| 7. Reset                               | .10 |

| 8. Program Memory (Flash)              | .11 |

| 9. Data Memory (SRAM)                  | .12 |

| 10. Calendar chip                      | .13 |

| 11. Memory and Calendar Backup Battery | .14 |

| 12. LCD                                |     |

| 13. Reader                             | .17 |

| 14. External Keyboard                  | .18 |

| 15. Membrane Keypad                    | .19 |

| 16. RS232 (COM1)                       |     |

| 17. RS232 (COM3)                       |     |

| 18. RS485                              |     |

| 18.1. Transmission Method              | .22 |

| 18.2. Cable                            |     |

| 18.3. Speed and Distance               | .23 |

| 18.4. Number Of Nodes                  | .23 |

| 18.5. Connection and Termination       | .23 |

| 18.6. Repeater                         | .24 |

| 18.7. Connector                        | .24 |

| 19. Digital Input / Output             | .25 |

| 19.1. Digital Output                   | .25 |

| 19.2. Digital Input                    | .26 |

| 19.3. Connector                        |     |

| 19.4. Loop Back Tester                 |     |

| 20. LED                                | .29 |

| 21. Speaker                            | .30 |

# **LIST OF FIGURES**

| Figure 1.  | Main Panel                   | 4   |

|------------|------------------------------|-----|

| Figure 2.  | Front Panel                  | 4   |

| Figure 3.  | Rear Panel                   | 5   |

| Figure 4.  | Left Panel                   | 5   |

| Figure 5.  | PCB                          | 6   |

| Figure 6.  | Main Power Connector         | 7   |

| Figure 7.  | Battery Pack Connector       | 7   |

| Figure 8.  | Power Circuit Diagram        | 7   |

| Figure 9.  | SRAM Connector               | .12 |

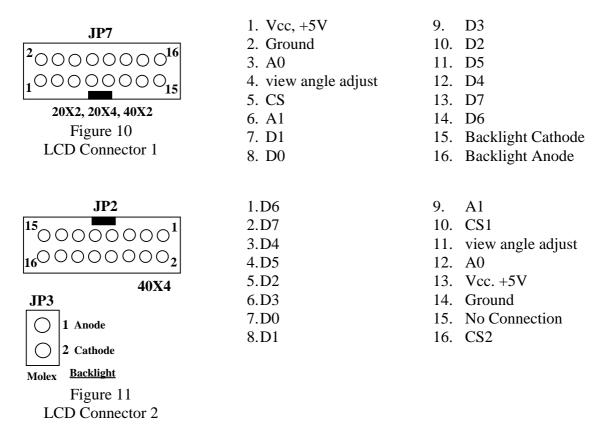

| Figure 10. | LCD Connector 1              | .15 |

| Figure 11. | LCD Connector 2              | .15 |

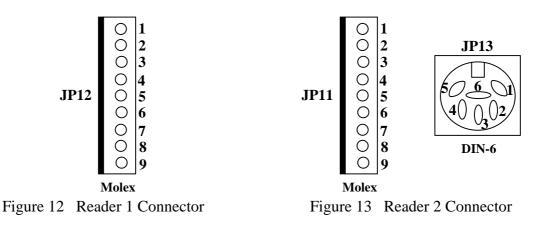

| Figure 12. | Reader 1 Connector           | .17 |

| Figure 13. | Reader 2 Connector           | .17 |

| Figure 14. | External Keyboard Connector  | .18 |

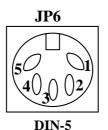

| Figure 15. | Keypad Connector             | .19 |

| Figure 16. | COM1 Connector               | .20 |

| Figure 17. | COM3 Connector               | .21 |

| Figure 18. | RS485 Transceiver            | .22 |

| Figure 19. | RS485 Typical Configuration  | .23 |

| Figure 20. | RS485 Connector              | .24 |

| Figure 21. | Digital I/O Diagram          | .25 |

| Figure 22. | Digital Input Example        | .27 |

| Figure 23. | Digital I/O Connector        | .28 |

| Figure 24. | Digital I/O Loop Back Tester | .28 |

| Figure 25. | LED Connector                | .29 |

# 1. Preface

This manual provides in-depth hardware informations of the Cipher-510 programmable terminal and serves as a reference for hardware and maintenance engineers. Assumption has been made that readers of this manual have basic knowledge of electric and/or electronic theory.

Numberings of all components, including connectors, passive and active components conform to the PCB V1.01. However, Syntech does not guarantee this conformity. The numberings and locations of components might be re-arranged. For confirmation, please refer to the PCB and its schematics. After all, this manual intends to describe the operation theory of the circuitry utilized.

## 2. <u>General Features</u>

The Cipher-510 is equipped with the followings,

- TLCS-900 16 bit CPU running at 9.8304 MHz

- Program : 128 KB flash memory

- Data memory : 128 KB to 512 KB SRAM (on an 128 KB base)

- Fine-tunable calendar chip

- Memory & calendar chip backup 3.6V NiCd battery

- 1.2V X 7, 1400mAh rechargeable NiCd battery for operation backup

- Battery/external DC voltage monitor circuit on-board

- Self-shutdown circuit on-board

- slot-type bar code input ports

- 2 reader ports for barcode scanners (Wand or Laser-emulation), or up to dualtrack magnetic card readers

- 20 characters by 2 lines LCD display with adjustable backlight and viewing angle

- standard 4 by 4 matrix membrane keypad (expandable up to 8 by 8)

- 2 photo-isolated digital input

- 2 photo-isolated digital output

- external keyboard port (AT keyboard)

- RS232 port X 2

- RS485 port

# 3. <u>Characteristics</u>

Basic characteristics of the Cipher-510 are listed below,

### 3.1. Electrical

- Main Power Supply Voltage : 12V ±5% DC (Unlike the Cipher-5000 series data terminal, this **MUST** be a regulated +12V DC)

- Power consumption : 0.5W maximum with LCD backlight off and no external devices attached

### 3.2. Environmental

- Humidity (operating) : non-condensed 20% to 90%

- Humidity (storage) : non-condensed 10% to 95%

- Temperature (operating) : 0 to 50 °C

- Temperature (storage) : -20 to 70 °C

- EMC regulation : FCC class A and CE approved

### 3.3. Physical

- Dimensions : 261 X 125 X 100 mm (including battery holder)

- Weight : 1 Kg including all batteries

- Material : ABS

- Color : Gray

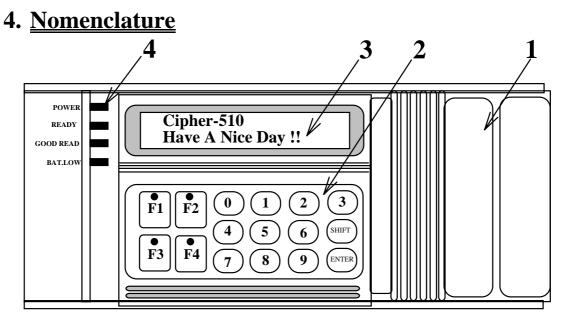

Figure 1 Main Panel

- 1. Slot-type reader

- 2. Membrane Keypad

- 3. LCD display

- 4. LED indicators, from top to bottom

- POWER (red)

- READY (yellow)

- GOOD READ (green)

- BATTERY LOW (red)

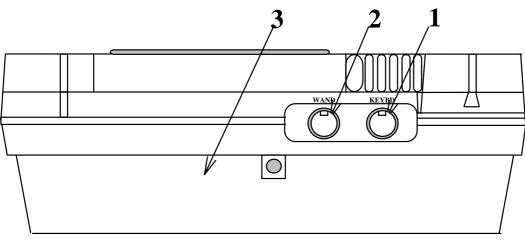

Figure 2 Front Panel

- 1. External AT keyboard

- 2. External Reader

- 3. Battery Holder

Figure 3 Rear Panel

- 1. Main power connector

- 2. RS232 port (COM1)

- 3. RS485 port

- 4. RS485 port

- 5. RS232 port (COM3) and digital input/output

- 6. Holes for fixing Battery clippers

- 7. Holes for screw

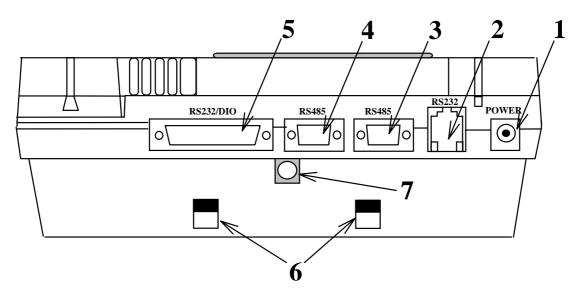

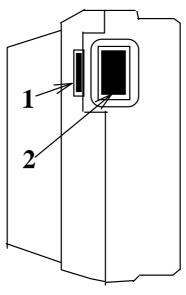

Figure 4 Left Panel

- 1. LCD viewing angle adjust

- 2. Power switch

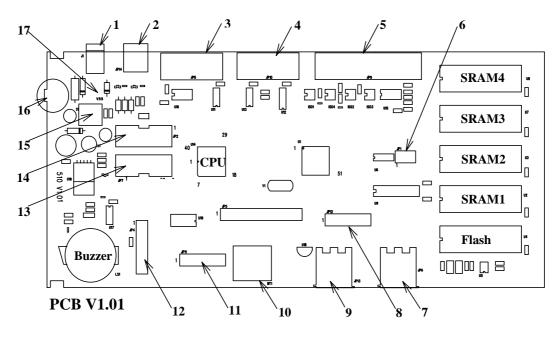

# 5. <u>PCB</u>

The PCB and locations of major components are shown below,

Figure 5 PCB

- 1. J1, External +12V DC

- 2. JP14, RS232 COM1

- 3. JP8, RS485

- 4. JP10, RS485

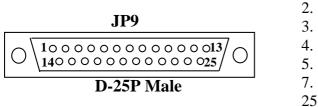

- 5. JP9, RS232 COM3 & Digital Input / Output

- 6. JP1, SRAM5-8 Chip Select

- 7. JP6, External Keyboard

- 8. JP12, Built-in Reader (READER 1)

- 9. JP13, External Barcode reader (READER 2)

- 10. 3.6V NiCd Battery

- 11. JP11, READER 2

- 12. JP12, LED

- 13. JP7, LCD connector for 20X2, 20X4, 40X2

- 14. JP2, LCD connector for 40X4

- 15. S1, Power Switch

- 16. VR6, view angle adjust variable resistor

- 17. Operation Backup Battery Connector

### 6. <u>Power Circuit</u>

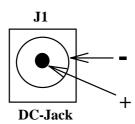

#### 6.1. Power Source

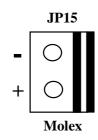

The 510 can be powered from 2 sources : the external +12V or operation backup battery. If line power was down, the 1400mAh NiCd battery pack then took the place to provide the system power. The switching from external DC power to the battery is accomplished by a simple pair of diodes and is not even noticed by the operator. However, loss of the main power can be seen from the POWER LED on the panel which will be described in detail later.

Figure 6 Main Power Connector

Figure 7 Battery Pack Connector

Figure 8 Power Circuit Diagram

D11 is a power schottky diode (1N5817 or the likes) which can provide lower forward voltage (0.2~0.5V) and thus get higher efficiency when using the battery. Whereas D9 is a general power diode (1N4001 or the likes) with voltage drop from 0.6~1.0V (depending on the current flowing through). However, its leakage current is much smaller than a Schottky type diode and thus prevents current from leaking back to the main power source or associated circuits when main power is down. Messing of these two diodes does not cause any operational fault, however, the performance and efficiency are degraded.

### 6.2. Switching Regulator

A simple buck-type switching regulator (LM2575) is used to generate the required system power (+5V). This regulator is capable of providing up to 1 Amp of current and provides a reasonable typical efficiency around 70% to 80%. Low-ESR (equivalent series resistance) type electrolytic capacitors are used both at input and output sides to reduce ripples. In effect, this regulator can accept input voltage from 7 to 20V. However, if the main DC was too low, the battery couldn't be charged. On the opposite side, it might damage the battery by providing a too high charge current.

The power is controlled via a dual pole single throw (DPST) type switch and R58 is used to discharge the output capacitor when switch was turned off (namely to the OFF side). As the 510 itself consumes very little power (typical 80mA with LCD backlight off and no external devices attached), this ensures a sharp power-up and power-down sequence.

### 6.3. Operation Battery

#### 6.3.1. Charging

The charging is not controlled by the power switch, as can be seen from the previous figure. The resistor R57 provides the path and control over the charge current when main power and the battery pack are both asserted. The battery pack is trickle charged at a typical of 30 mA current. For a charging efficiency of 80 %. The battery can be fully charged from drained in 1400/(30 X 80 %) = 59 hours ~= 2.5 days.

#### 6.3.2. <u>Maintenance</u>

Normally, the NiCd battery is guaranteed to work for 300 charge/discharge cycles while preserves at least 60% of its original capacity. However, it features a self-discharging characteristic even when it is disconnected. After a long-term storage (even when it is new), several charge/discharge cycles should be exercised to restore its specified capacity. The battery pack used can be quick charged at 1C rate (1700mA/Hour). On the shelf battery chargers can be used for this purpose. However, it is recommended to use up to 1Amp current and make sure that the charger provides cutoff methods such as V, V/t and so on. If there is any questions, please consult Syntech.

#### 6.3.3. <u>Protection & Shutdown</u>

The typical voltage for a NiCd battery cell is 1.2V and can be charged up to 1.4V or even 1.5V if it is quick-charged. This is immaterial for the charging circuitry as the charge current became smaller when the battery is about to be full. As long as the charge current is within the specified trickle charge current limit (0.04 C), the battery will not be damaged. However, deep discharging the battery degrades its useful life or even cause permanent damage such as polarity reversal. A monitoring and shutdown circuitry is used to prevent this from happening. The battery voltage is feed to the CPU on-chip ADC via a resistor divider and then is checked by the program. If the voltage is about to be drained, the BATTERY LOW LED will be flashing for warning. And finally, if the battery was drained, the system will shutdown the system power.

During the discharging cycle (from fully charged to drained), the battery voltage drops rapidly at the beginning and then stays around 1.2V during most of the cycle (~70%). Finally when it is about to be drained, the voltage starts to drop again. Unfortunately the battery voltage alone is not sufficient to decide the remaining capacity of the battery. The recommended voltage level is 1.1V per cell for battery low and 1.0V for drained. That is, if the whole battery pack drops to below 7.0V, it is considered to be drained and the system power will be shutdown.

The shutdown is accomplished by a Flip-Flop and its glue circuits. Its output is reset to low (power enabled) during power on. A CPU output pin can then set it to high (to shutdown the switching regulator) by sending a negative going pulse. An R-C network prevents power-on spikes to false-trigger the circuit by disabling it for the starting 50ms. After shutdown, this Flip-Flop is still powered to keep this shutdown signal, which however consumes very little current. The shutdown signal stays even if the main power is asserted again. To restart the machine, the power switch must be turned off and then on again.

## 7. <u>Reset</u>

The system reset signal is generated by a voltage detector chip RICO RE5V (or compatible chips). It outputs an active low reset signal when the system power drops below a pre-determined voltage level (Vdet-). The reset signal then changes to high when the power is higher than another pre-determined voltage level (Vdet+). The Vdet+ is about 200 mV higher than Vdet-. This is known as hysteresis, and it prevents noise from false-triggering the reset circuitry. The TLCS-900 is guaranteed to work within 5V  $\pm$ 10%, and the Vdet- is set to 4.6V. This reset signal does not only ensure the proper operation of the CPU but also is used to reset the UART chip (NS82C50) and control SRAM access (connecting to SRAM CE2) during power-up and power-down. The later is very important as the SRAM contents might be changed by unwanted spikes during supply voltage changes.

### 8. Program Memory (Flash)

128 Kbytes flash memory (U4) is used to store the program code and is guaranteed to last at least 100,000 erase/program cycles. Two kinds of flash chips can be used, the AMD 29F010 and 28F010 from Intel, MX and so on, and the access time must be 150 ns or faster. The former is a pure +5V device whereas the later requires a +12V for erasing/programming. U5 and accompanying passive components are used to generate this +12V. The U5 can be a Maxim MAX662 or Linear Technology LT1262, which two are totally compatible. Instead of inductor-type switching DC/DC converter, these chips utilize a capacitor switching circuitry and feature smaller PCB space, lower ripple, and lower EMI emission.

The +12V generation is controlled by a CPU output pin and the types of flash memory installed is automatically identified by software (refer to software manual, routine download()). That is, if 29F010 is used, this circuit is not enabled. During normal read, this DC/DC converter is disabled and the voltage stays at 0V.

## 9. Data Memory (SRAM)

The TLCS-900 is capable of directly addressing up to a total of 16 Mbytes of memory. However, due to limited PCB space and application needs, the 510 provides up to 1 Mbytes SRAM for data storage. The CPU on-chip chip select signal (CS0) is set to this memory area and then further decoded by the 74HC138 to generate 8 chip select signals. That is, this 1 Mbytes space is subdivided into 8 partitions with 128 Kbytes each. Depending on application needs, one or up to 8 SRAMs can be used. However, they must be added sequentially from the start and then they can be correctly recognized by the software. The sequence is U2, U3, U7 then U8 (on the PCB, from lower-right to upper-right). Due to limited PCB space, only 4 sockets are provided, if more than 4 SRAMs are to be used, rest of the SRAMs can be piggy-backed on U2 to U8 and then connect their chip select pins to JP1.

| JP1        |   |    |        |

|------------|---|----|--------|

| $\bigcirc$ | 1 | 1. | SRAM 5 |

| $\bigcirc$ | 2 | 2. | SRAM 6 |

| $\bigcirc$ | 3 | 3. | SRAM 7 |

| Molex      | 4 | 4. | SRAM 8 |

Figure 9 SRAM Connector

The SRAM used must be LL type for reducing battery power consumption and with access time 150 ns or faster. These SRAMs are backup by a NiCd battery and will be described in detail later.

# 10.<u>Calendar chip</u>

A battery backup calendar chip is used to retain the system time even when power is off. The chip utilized is a V3022 from EM micro-electronic Marin SA. It features the following outstanding features,

- Very low power consumption

When powered from the battery (3.6V), the current is typically 0.9μA.

- Wide operation voltage range This chip works down to 2V.

- On-chip high precision oscillator This is a must for accurate time keeping. The oscillator is built-in inside the chip and is factory trimmed.

- Timer Adjustment

It can also be fine tuned to compensate for a fast or slow clock. This is an outstanding feature for those applications which need absolute accurate system time such as a time/clock application. The tuning of the calendar chip is done by modifying the value of the **trimming register** of the calendar chip.

• Trimming Register

The speed of the calendar chip can be tuned in units of ppm via a digital trimming register. The trimming range is from 0 to 255 ppm. The bigger the value of the trimming register the slower the calendar chip runs. For instance, if the calendar chip is 1 second **slow** in one day then the value of the trimming register should **decrease** 12 to correctly adjust the calendar chip. During system initialization, this register is set to 186.

$1 \text{ sec} / 1 \text{ day} = 1000000 / (24 \text{ hours } * 60 \text{ min } * 60 \text{ sec}) = 11.57 \text{ ppm} \sim = 12 \text{ ppm}$

• Write-protected

The time and trimming register are write-protected, and they won't be changed accidentally.

#### • Cold start detection

There is a cold start bit in the chip. This bit is set if power loss encountered or on first power-on. The software can then recognize this bit and initialize the calendar chip.

### 11.Memory and Calendar Backup Battery

A 3.6V rechargeable NiCd battery is used to backup the SRAM and keeps the calendar chip running even when system power is off. Its capacity is 60 mAh and is trickle charged with a typical 1.2 mA current. After fully charged, it is able to sustain for more than 4 months. For example, if 4 SRAMs,

- SRAM (LL-type, SONY CXK581000)

- current consumed is 0.7µA (typical) and 4µA (max, 0 to 40°C)

- V3022 : 0.9µA (typical), 1.5µA (max.)

Time (typical) = 60 mAh / (0.7 \* 4 + 0.9) = 16216 hrs = 675 days > 22 monthsTime (worst) = 60 mAh / (4.0 \* 4 + 1.5) = 3428 hrs = 142 days > 4 months

The switching between +5V and battery is done by 2 transistors and some passive components. This circuit features a very low leakage (base to collector leakage current of the PNP transistor Q11) back to 5V and a low voltage drop (saturated Vce is ~0.2V). This low voltage drop is necessary for most CMOS chips. (If you are interested in this issue, please refer to any CMOS data book.) When system power is supplied, the supply voltage for these chips (SRAM & calendar) is +5V minus Vdrop. Whereas other signals are directly from/to CPU and other chips, which are supplied with +5V. However, for SRAM (a CMOS chip), the upper limit of input signal is Vdd + 0.5V. If diodes such as 1N4148 is used for switching, the voltage drop is also 0.6V which is too large and will damage these chips.

# 12.<u>LCD</u>

The standard display for Cipher-510 is 20 characters by 2 lines LCD. However, up to 40 by 4 LCD can be attached.

For the standard 20X2 LCD, a flat cable is used to connect the LCD module to the main PCB (JP7). The JP7 is etched and can't be inserted in wrong ways, but not on the LCD module side. Remember to plug the **RED** side into **pin #1** of the LCD module connector. (same as Cipher-5000 series).

The LCD is equipped with LED backlight and can be tuned into 4 levels. Two high current NPN transistors (Q3 and Q6, 500 mA maximum) are used to drive the backlight and Q3 provides twice the current as Q6 does. Controlling Q3 & Q6 yields current ratios to be 0, 1, 2 or 3. To accommodate different LCD size (larger panel requires more current to drive), through-hole resistors (R26, R27 & R29) are used. If higher current is required, replace them with same value resistors to keep the current ratio. Normally, for 20 by 2 LCD, these resistors are  $20\Omega$  and the current is,

Ibacklight = (Vcc - Vce (saturated) - Vf) / R Where, Vcc : supply voltage (+5V) Vce (saturated) : transistor collector to emitter saturation voltage Vf : LED forward voltage R : resistor The typical backlight current is then (5 - 0.2 - 3.8) / 20 = 50 mA. That is, from 0 to 150 mA on a 50 mA basis. Also, the viewing angle can be manually adjusted via a variable resistor (R6) which locates adjacent to the power switch.

## 13.<u>Reader</u>

There are total 2 reader ports provided, each can be either a Barcode slot reader, Barcode Scanner (Wand/Laser emulation), or up to dual-track magnetic card reader. They are equivalent in both hardware and software. However, Cipher-510 assumes that one of them is a built-in slot-type reader (READER 1) whereas the other is an external attached scanner (READER 2). Their connectors and pin-assignments are listed below. Beware that, in order to decode barcode and magnetic card at the same time, some signals share the same pin. However, the software is able to tell which type of the readers are attached.

| JP11 & 12 | Barcode       | Magnetic | <b>DIN-6 (JP13)</b> |

|-----------|---------------|----------|---------------------|

| 1         | Start Of Scan | Not used | 5                   |

| 2         | Data          | Clock 1  | 2                   |

| 3         | Good Read     | Not used |                     |

| 4         | Not Used      | Data 1   |                     |

| 5         | Switch        | Clock 2  | 4                   |

| 6         | Power Enable  | Not used | 6                   |

| 7         | Ground        | Ground   | 3                   |

| 8         | Not used      | Data 2   |                     |

| 9         | Vcc, +5V      | Vcc, +5V | 1                   |

As there are not so many pins in JP13, the external reader, i.e. READER 2 is limited to barcode readers only.

# 14. External Keyboard

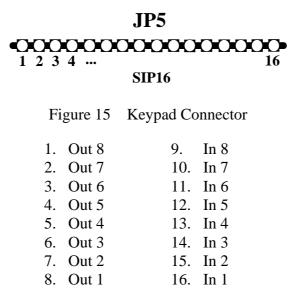

Besides the built-in membrane keypad, an external AT-compatible keyboard can be attached for handy data entry. The connector and pin assignment conforms to PC/AT standard keyboard.

- 1. clock

- 2. ground

- 3. data

- 4. +5V

- 5. No connection

Figure 14 External Keyboard Connector

### 15. Membrane Keypad

A standard 16-key membrane keypad is provided for data entry. However, 8 by 8 scanning circuits are supported. To efficiently utilize the system resource, the out pins are also used to drive LEDs.

To use the standard keypad, plug the 8-pin connector to center of this 16-pin connector, that is, pin 5 to pin 12 of JP5.

### 16.<u>RS232 (COM1)</u>

Besides the data signals, the COM1 also provides RTS and CTS signals for handshaking.

- 1. No Connection

- 2. Ground

- 3. RTS

- 4. CTS

- 5. Receive data

- 6. Transmit data

A simple loop back test kit can be used for diagnostic as follows, (please refer to 510 sample program self-test routine)

- Transmit data shorts to receive data

- RTS shorts to CTS

### 17.<u>RS232 (COM3)</u>

Besides the data signals, the COM1 also provides RTS and CTS signals for handshaking. The connector and pin-assignments are depicted below. Beware that it shares the same connector with digital input/output.

Figure 17 COM3 Connector

- 2. Transmit data

- . Receive data

- 4. RTS

- 5. CTS

- 7. Ground

- 25. +5V

A simple loop back tester can be used for diagnostic as follows, (please refer to 510 sample program self-test routine)

- Transmit data shorts to receive data

- RTS shorts to CTS

# 18.<u>RS485</u>

RS485 is a widely used EIA standard suitable for multi-drop communications. For clarity, a comparison to RS232 is made as follows,

| Features             | RS485                     | RS232                 |

|----------------------|---------------------------|-----------------------|

| Modes of operation   | double ended              | single ended          |

| Maximum data rate    | 10 Mbps                   | 115,200 bps or higher |

| distance             | 4000 feet                 | 50 feet               |

| Number of drivers &  | 32 drivers, 32 receivers  | 1 driver,1 receiver   |

| receivers allowed on |                           |                       |

| one line             |                           |                       |

| cable                | non-shielded twisted pair | shielded cables       |

| Driver output        | -7V to 12V                | 25V                   |

| maximum voltage      |                           |                       |

| Receiver input       | 200mV                     | 3V                    |

| sensitivity          |                           |                       |

These features are further described below,

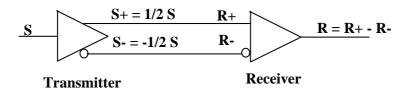

#### **18.1.** Transmission Method

Theoretically, for two adjacent lines, noises induced from whatever cause should be the same. If a signal and its complement are transmitted together, then on the receiving side, a differential circuit can be used to remove noises and restore the original signal.

Figure 18 RS485 Transceiver

For the figure above, assume a noise N is induced, then

$R = R_{+} - R_{-} = (S_{+} + N) - (S_{-} + N) = (1/2 S_{+} - 1/2 S_{-}) = S$

Unlike RS232, differential (double ended) signals are transmitted which provides higher noise immunity compared to single ended methods. Thus higher speed and longer distance can be achieved.

### 18.2. Cable

To get the optimum noise immunity, twisted pair cable is used, as the two signal lines do not only adjacent to each other but also cross-sectional mixed together. More precisely, according to the RS485 standard, inexpensive AWG #24 twisted pair should be used. Under most cases the shielding is not so effective. In effect, if the distance (cable length) is long, the shielding tends to increase the overall cable capacitance and

thus degrades the performance (the capacitance is an AC load to the drivers, and if it is too large, it will limit the slew rate and distorted signals).

#### 18.3. Speed and Distance

According to the standard, the maximum allowable distance is inversely proportional to the transmission speed.

C = d \* v

where

$C = constant, 10^8 bps m$ d = overall distance in meters (up to 1000 m)

v = bits per second

Beware that the maximum allowable distance is 1 km, that is, for data rates lower than 100 Kbps, the allowable distance is always 1 km. For Cipher-510, the speed is 75 Kbps and thus the maximum allowable distance is 1 km.

### 18.4. Number Of Nodes

The RS485 transceiver utilized by Cipher-510 complies with the EIA standard and thus allows up to 32 transceivers on the line, where a transceiver equals one driver plus one receiver.

This 32 comes from hardware limitations, not software. Each receiver on the line represents a load to the driver, and 32 is the driving capability of the driver. However, some transceiver vendors claim that they reduce the effective load of the receiver and thus allow up to 128 transceiver on one line. Note that, this method can not improve the allowable maximum distance, it remains the same.

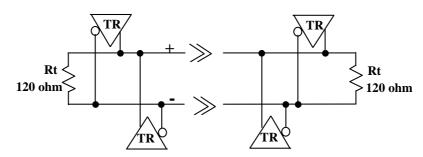

### **18.5.** Connection and Termination

The typical RS485 configuration is depicted below,

Figure 19 RS485 Typical Configuration

In configuring an RS485 communication line, the followings should be noted,

- DO NOT fork the connection and it should never be star-linked. That is, there are two and only two ends of the communication line.

- Attach 2 termination resistors,  $120\Omega$  at each end.

According to the transmission line theory, as the signal propagates through the wire, it must be appropriately terminated at the ends to absorb the energy. Or else it will reflect back and superimpose with the signal itself. To effectively absorb the energy, resistors with values identical to the characteristic impedance of the cable are attached to each end of the cable. In this case, the characteristic impedance of AWG#24 twisted-pair cable is 120. If the configuration has more than 2 ends then it cannot be appropriately terminated. And that's why it should not be star-linked.

#### 18.6. Repeater

If more than 32 stations or longer distance are required, repeaters can be used. Physically, the repeater separates the communication line into two individual RS485 lines and each preserves its own characteristics. That is, allowable distance for each is 1 km and allowable number of transceivers is 32 (remember the repeater itself takes 1).

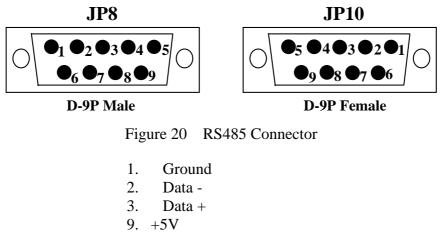

### 18.7. Connector

This port intentionally occupies two connectors, that is same signals are connected to these two connectors. As one of them is male and the other one is female, if a machine is to be removed from the net for maintenance, cables from previous station can directly connects to the cable goes to the next station and the net remains unaffected.

Others : No Connection

Unlike RS232, the RS485 transceiver features an inherent loop back function and no loop back tester is needed for diagnostic. That is, the loop back test not only tests the UART but also tests the transceiver chip. However, beware that during loop back test, the cable must be removed, or it will interfere or be interfered by other stations on the net.

# 19.<u>Digital Input / Output</u>

The Cipher-510 provides 2 digital inputs and 2 digital outputs for controlling and monitoring external devices. These inputs and outputs are photo-isolated.

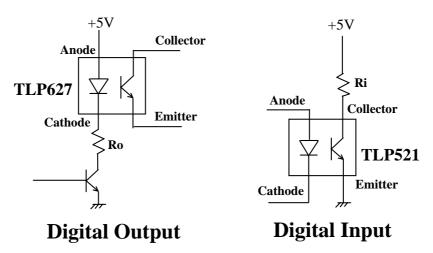

Figure 21 Digital I/O Diagram

### **19.1. Digital Output**

The digital output points are photo-isolated by a photo-transistor : TLP627. It features a Darlington output with a minimum current transfer ratio of 1000%. It means that if 1 mA current flows through the internal IR LED, the output transistor is guaranteed to supply at least 10 mA current. Characteristics of the TLP627 are listed below,

- 1) LED

- Maximum Forward current : 60 mA

- Pulse forward current : 1A

- Power dissipation : 100 mW

- Maximum reverse voltage : 5V

- Forward voltage (at 10 mA) : 1.15V (typical), 1.3V (maximum)

- Reverse current : 10 µA (maximum)

#### 2) Output Transistor

- Collector-Emitter breakdown Voltage : 300 V

- Emitter-Collector breakdown Voltage : 0.3 V

- Maximum Power dissipation : 150 mW

- Collector dark current (at 25°C) : 200 nA maximum

- Collector dark current (at 85°C) : 20µ A maximum

- Current transfer ratio : 4000% (typical), 1000% (minimum)

- Isolation resistance :  $5*10^{10}\Omega$  (minimum),  $10^{14}\Omega$  (typical)

- Isolation Voltage : 5000 Vrms (minimum)

The Ro chosen is 300 and the output current is, Io = (+5V - Vf - Vce ) \* T / Ro where,

T = current transfer ratio Io = output current Vf = LED forward current Vce = collector to emitter voltage

#### **19.2. Digital Input**

The digital inputs are photo-isolated by the photo-transistor : TLP521. Its characteristics are listed below,

- 1) LED

- Maximum Forward current : 70 mA

- Pulse forward current : 1 A

- Maximum reverse voltage : 5V

- Forward voltage (at 10 mA) : 1.15V (typical), 1.3V (maximum)

- Reverse current : 10µ A (maximum)

2) Output Transistor

- Collector-Emitter breakdown Voltage : 35 V

- Emitter-Collector breakdown Voltage : 7 V

- Maximum Power dissipation : 150 mW

- Maximum collector current : 50 mA

- Collector dark current (at 25°C) : 100 nA maximum

- Collector dark current (at 85°C) : 50µA maximum

- Current transfer ratio : 100%(minimum), 600% (maximum)

- Isolation resistance :  $10^{11}\Omega$  (typical)

- Isolation Voltage : 2500 Vrms (typical)

The transistor collector is pulled up by Ri, a 10K resistor and then feed to CPU input pin, which features a low threshold of 0.8V and high threshold of 2.2V. That is, the collector voltage must be no more than 0.8V to be treated as *low* and no lower than 2.2V to be treated as *high*.

#### 19.2.1. <u>Input High</u>

Ideally, when there is no current flowing through the input LED, the output transistor is off and the collector is pulled up to +5V. However, leakage current does exist. Assume a small leakage current flows through the LED then,

collector voltage Vc =  $+5V - (Ic * Ri) \ge 2.2 V$

where Ic is the collector current and = collector dark current + ( LED leakage current \* current transfer ratio)

The lowest collector voltage(worst case) =  $5.0 - ((50\mu A + (IL * 600\%) * 10 K))$

5 V - 0.5 V - 60000 \* IL  $\geq$  2.2 V and IL  $\leq$  38  $\mu A$

That is, the leakage current into the LED should not be larger than  $38\mu A$ , however this is much higher than the LED leakage current 10  $\mu A$  and false trigger is not likely to happen.

#### 19.2.2. <u>Input Low</u>

To input a low, the external device must supply a large enough current to flow through the LED to turn on the transistor and pull collector no higher than 0.8V. This LED current can be calculated similar to the case for input high.

$5V - 0.5V - (100\% * IL * 10K) \le 0.8 V$  then  $IL \ge 0.37 \ mA$

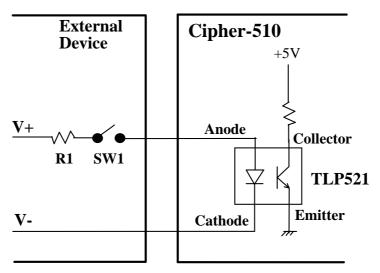

That is, to pull the digital points low, there must be at least 0.37 mA current flowing through the LED. For example, to connect an external dry contact to the digital inputs,

Figure 22 Digital Input Example

LED current IL =  $(V_+ - V_- - V_f) / (R_1 + R_{on}) = 0.37 \text{ mA} = 1 \text{ mA}$  (safe margin) Where

$V_+$ : positive supply voltage of the external device

$V_{\mbox{-}}\,$  : negative supply voltage of the external device

$V_f$  : LED forward voltage

$R_1$  : current setting resistor

Ron : switch contact resistance

If  $(V_+ - V_-) = 5V$  and maximum  $R_{on}$  is  $10\Omega$  then,  $(5 - 1.3) / (R_1 + 10) \ge 1$  mA,  $R_1 \le 3.7 K\Omega$

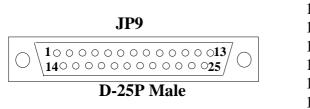

#### **19.3.** Connector

Digital Inputs / Outputs share the same connector as the COM3.

Figure 23 Digital I/O Connector

- 9. Output 0 Emitter

10. Output 0 Collector

11. Output 1 Emitter

12. Output 1 Collector

13. Input 0 Cathode

14. Input 0 Anode

15. Input 1 Cathode

- 16. Input 1 Anode

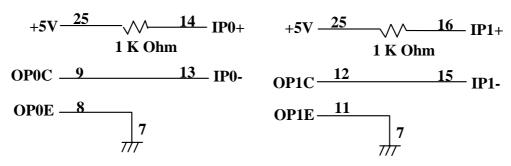

#### **19.4.** Loop Back Tester

A simple loop back tester can be used for self-diagnostics as shown below.

Figure 24 Digital I/O Loop Back Tester

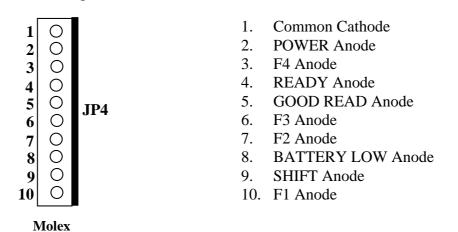

### 20.<u>LED</u>

There are totally 9 LEDs on the panel for showing system status.

- POWER (Red)

- READY (Yellow)

- GOOD READ (Green)

- BATTERY LOW (Red)

- F1 to F4 (Red)

- SHIFT (Red)

Except the POWER LED, all the other LEDs are controlled by software. Regardless of the power switch, the POWER LED is lit as long as power is asserted from the external DC jack. That is, even power switch is off, the POWER LED is lit.

Figure 25 LED Connector

To efficiently utilize system resources, the LED and keypad scanning circuitry occupies the same output pins. As the keypad is scanned per 10 ms, one control pin "\_LED\_ENABLE" is used to disable LED during keyboard scanning. However, as this period is so short that it is invisible to human eyes.

### 21.<u>Speaker</u>

A low power speaker is supported and 4 different volumes can be selected. This speaker electrically behaves like a capacitor, which implies that current flows only when states are changed (charge/discharge capacitor) and very little power is consumed. However, a higher voltage, e.g. 10V is needed to drive it. To do this, the speaker is driven by a pair of complementary CMOS-level 5V signals to produce a virtually 10V peak to peak signal across the speaker. This peak to peak voltage level is altered to control the volume. Up to 4 volume levels can be set and the corresponding peak to peak voltages are 2.5V, 5V, 7.5V and 10V. The working frequency ranges from 1KHz to 6KHz and have a peak volume around 4 KHz of frequency.